Objetivo:

Implementar el stack del

protocolo MQTT en un FPGA Virtex 4. Los métodos desarrollados en hardware son

conectar, publicar y subscribir. Desarrollar la comunicación wifi por medio del

módulo esp8266, control de pantalla OLED 64x128, y demás periféricos como

switches y relojes. Desplegar el servidor broker mosquitto para gestionar la

comunicación endpoint con el FPGA. Desarrollar un Skill Alexa para ejecutar los

comandos por voz y el procesamiento de los algoritmos de comunicación y

conexión MQTT en la nube con el servidor Lambda.

Introducción:

MQTT es un protocolo

abierto, sencillo, ligero y fácil de implantar.

Es ideal para responder a las siguientes necesidades:

Es ideal para responder a las siguientes necesidades:

- Está especialmente adaptado para utilizar un ancho de

banda mínimo

- Es ideal para utilizar redes inalámbricas

- Consume muy poca energía

- Es muy rápido y posibilita un tiempo de respuesta

superior al resto de protocolos web actuales

- Permite una gran fiabilidad si es necesario

- Requiere pocos recursos procesadores y memorias

El MQTT no es el

único protocolo que intenta imponerse: otros como XMPP, REST API y CoAp también

tienen ciertas ventajas.

MQTT:

¿cómo funciona?

MQTT es un servicio de publicación/suscripción

TCP/IP sencillo y sumamente ligero. Se basa en el principio cliente/servidor.

El servidor, llamado broker, recopila los

datos que los publishers (los objetos comunicantes) le transmiten. Determinados

datos recopilados por el broker se enviarán a

determinados publishers que previamente así se lo hayan solicitado

al bróker.

El principio de intercambio se parece mucho al de

Twitter. Los publishers envían los mensajes a un canal

llamado topic. Los subscribers (suscriptores) pueden leer esos

mensajes. Los topics (o canales de información) pueden estar

distribuidos jerárquicamente de forma que se puedan seleccionar exactamente las

informaciones que se desean.

Los mensajes enviados por los objetos comunicantes

pueden ser de todo tipo, pero no pueden superar los 256 Mb.

1.- Control exacto y sincronización de la señal de

reloj y registros.

2.- Implementar stack MQTT.

3.- Manejo del ESP8266

4.- Control de pantalla OLED 128x64, switches, leds,

etc.

5.- debug usb.

Metodología:

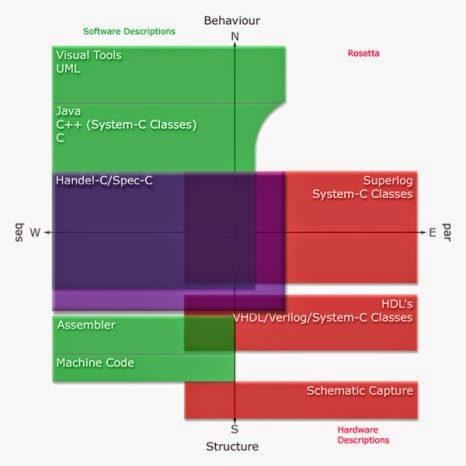

La descripción del Hardware se hará en

lenguaje C utilizando para ello una metodología propietaria de integración de

herramientas.

Nota:

El stack del protocolo MQTT fue implementado y

validado antes de la implementación en el FPGA en un microcontrolador microchip

en lenguaje C de tal forma que se partiera de una base confiable de

funcionamiento.

Destacar que el ciclo completo de diseño desde la

simulación hasta la implementación en el FPGA es en minutos. Esto quiere decir

que por cada cambio que haga en el código a nivel descripción de hardware hasta

la puesta en marcha se hace de manera secuencial y casi sin intervención. Ya

que las herramientas son muy configurables y se atan unas a otras.

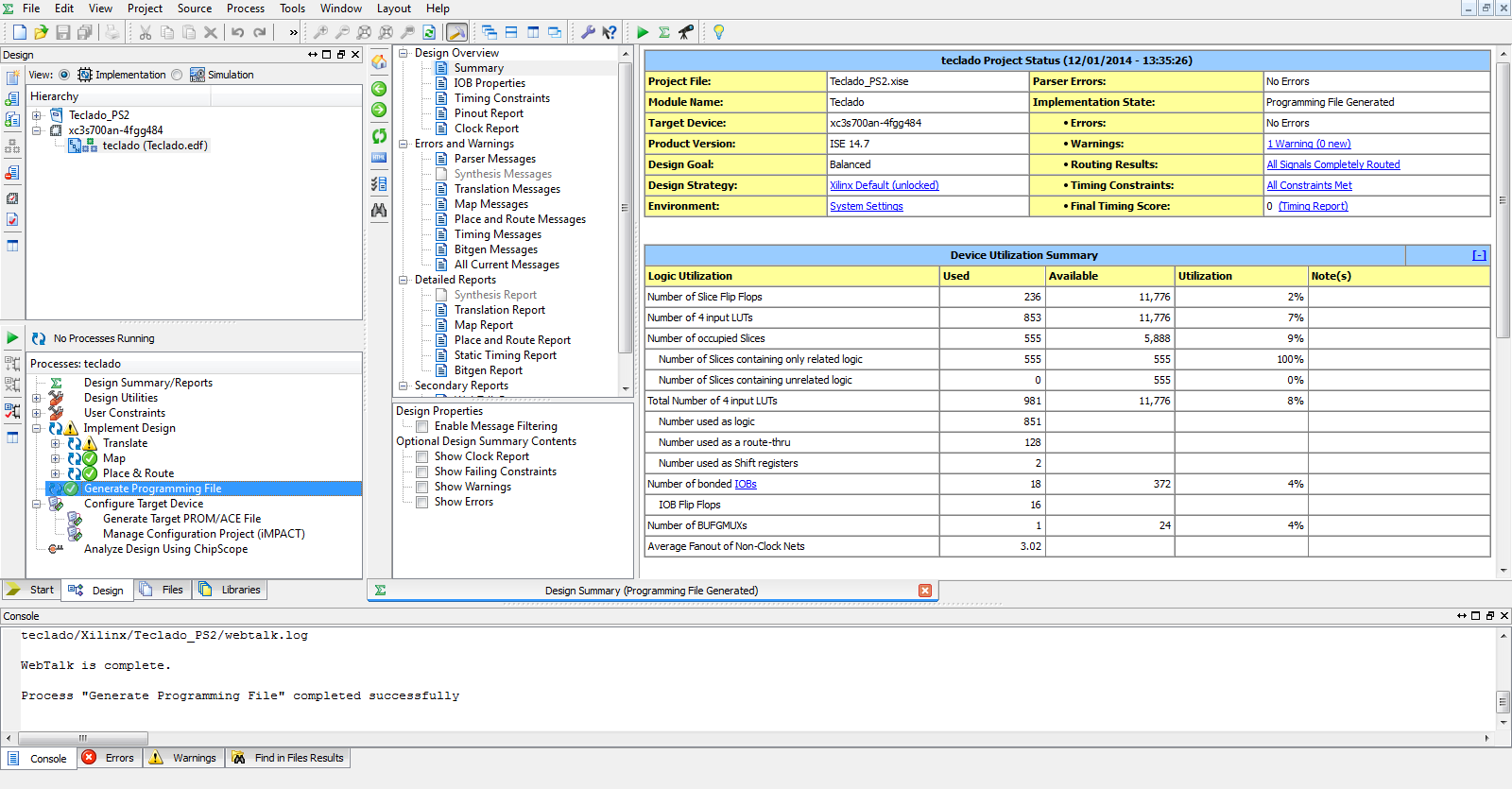

El flujo de secuencia y metodología usando diversas

herramientas se puede ver en la siguiente figura.

Herramientas

a utilizar:

FPGA:

1.- DK Design Suite 5.0. Plataforma

de validación rápida y eficiente para diseñadores que utilizan lenguaje C/C++

2.- Synplify Pro H-2013. Software de síntesis estándar en la

industria para FPGA de alto rendimiento.

3.- Xilinx Design Tools ISE Suite 14.7. Plataforma

de flujo de diseño completo para los FPGA de xilinx

PC:

1.- Mosquitto broker. Agente de mensajes de código abierto (con licencia EPL / EDL)

que implementa el protocolo MQTT versiones 5.0, 3.1.1 y 3.1. Mosquitto es

liviano y es adecuado para usar en todos los dispositivos, desde computadoras

de una sola placa de baja potencia hasta servidores completos.

2.- Alexa SDK. Es el servicio de voz ubicado

en la nube de Amazon disponible en los dispositivos de Amazon y dispositivos de

terceros con Alexa integrada. Con Alexa, se puede crear experiencias de voz

naturales para ofrecer a los clientes una forma más intuitiva de interactuar

con la tecnología que usan a diario. Gracias a su conjunto de

herramientas, APIs, soluciones de referencia y documentación, cualquier persona

puede crear skills de forma sencilla con Alexa.

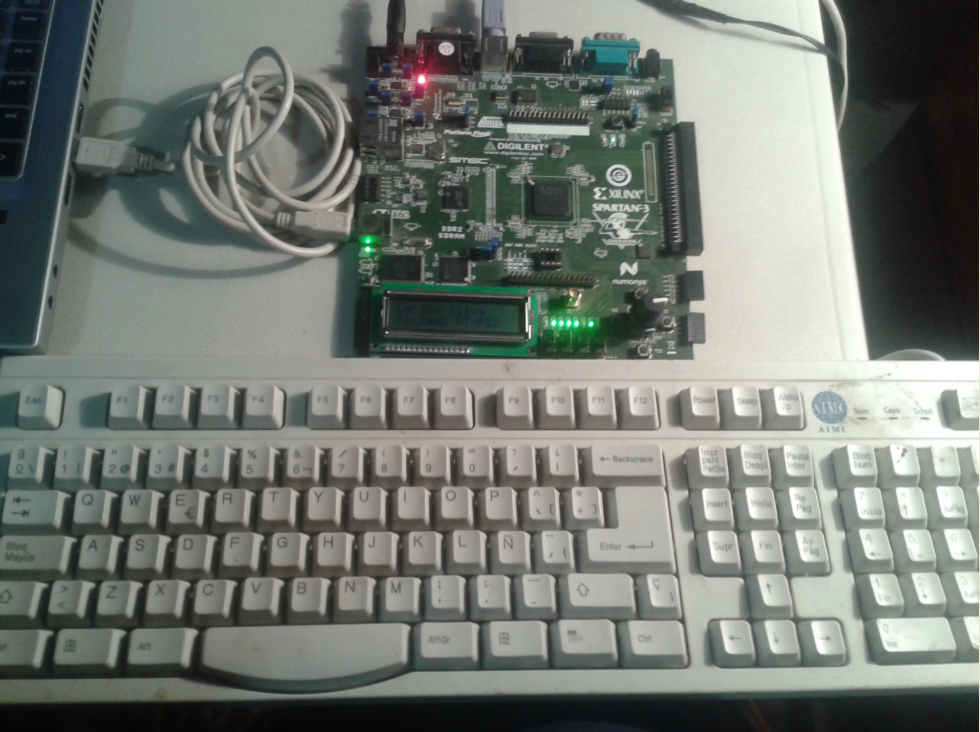

En

la siguiente figura se muestra en forma general el flujo de diseño del proyecto

y sus diferentes componentes:

1) Desarrollo del software para el Virtex 4 en la plataforma DK Design Suite:

2) Síntesis e implementación del diseño en el FPGA Virtex 4:

3) Alexa SDK

4) Conexión del FPGA:

5) Conclusiones:

Se logró satisfactoriamente hacer la implementación

del protocolo MQTT en el FPGA y el desarrollo de la skill de Alexa para el

monitoreo y control de las variables internas del Virtex 4.

6) Video demostrativo: