- En la literatura existen innumerables

ejemplos de uso de lenguajes de alto nivel para la descripción de Hardware.

Se mencionan algunos como los siguientes:

•

C-Based System level languages

•

Commercial

•

SystemC -- The Open SystemC Initiative

•

Handel C -- Celoxica Ltd.

•

Impulse C -- Impulse Accelerated Technologies

•

Carte C – SRC Computers

•

Research

•

Streams-C -- Los Alamos

National Laboratory

•

SA-C -- Colorado State

University, University of California, Riverside, Khoral Research, Inc.

•

SpecC – University of

California, Irvine and SpecC Technology Open Consortium

•

Matlab-based

•

AccelChip DSP Synthesis --

AccelChip

•

System Generator for DSP --

Xilinx

•

GUI Data-Flow based

•

Corefire -- Annapolis

Microsystems

•

Java-based

•

Commercial

•

Forge -- Xilinx

•

Research

•

JHDL – Brigham Young University

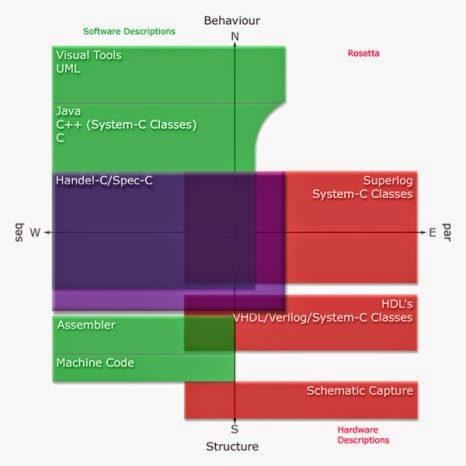

- En la metodología de DK Handel-C, la

siguiente figura muestra en qué posición se encuentra comparado con otros

lenguajes tanto de descripción en HW como meramente de SW.

Ventajas de Handel-C

·

Muy

fácil de aprender y usar

·

Las

instrucciones son basadas en ANSI C

·

Oculta

detalles complejos de implementación

·

Muy

flexible, no tiene limitaciones en paralelismo y tipos de datos.

·

Tiene

operadores extendidos para la manipulación de bits

·

Tiene

un modelo de tiempos bien definido

·

Tiene

diversidad de dispositivos FPGA abarcados

·

Códigos

heredados de lenguaje C previos son portados con facilidad.

·

Cada

asignación toma un ciclo de reloj en ser ejecutada.

- La

metodología DK Handel-C se muestra en la siguiente figura:

- Ejemplo de la metodología:

El ejemplo consistirá en realizar un

sumador de 8 bits utilizando para ello un CORE VHDL llamado AddVHDL.vhd cuyo

código fuente es:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity AddVHDL is

Port ( x

: in STD_LOGIC_VECTOR

(7 downto 0);

y : in STD_LOGIC_VECTOR (7 downto 0);

z : out STD_LOGIC_VECTOR (7 downto 0));

end AddVHDL;

architecture Behavioral of AddVHDL is

begin

z

<= x + y;

end Behavioral;

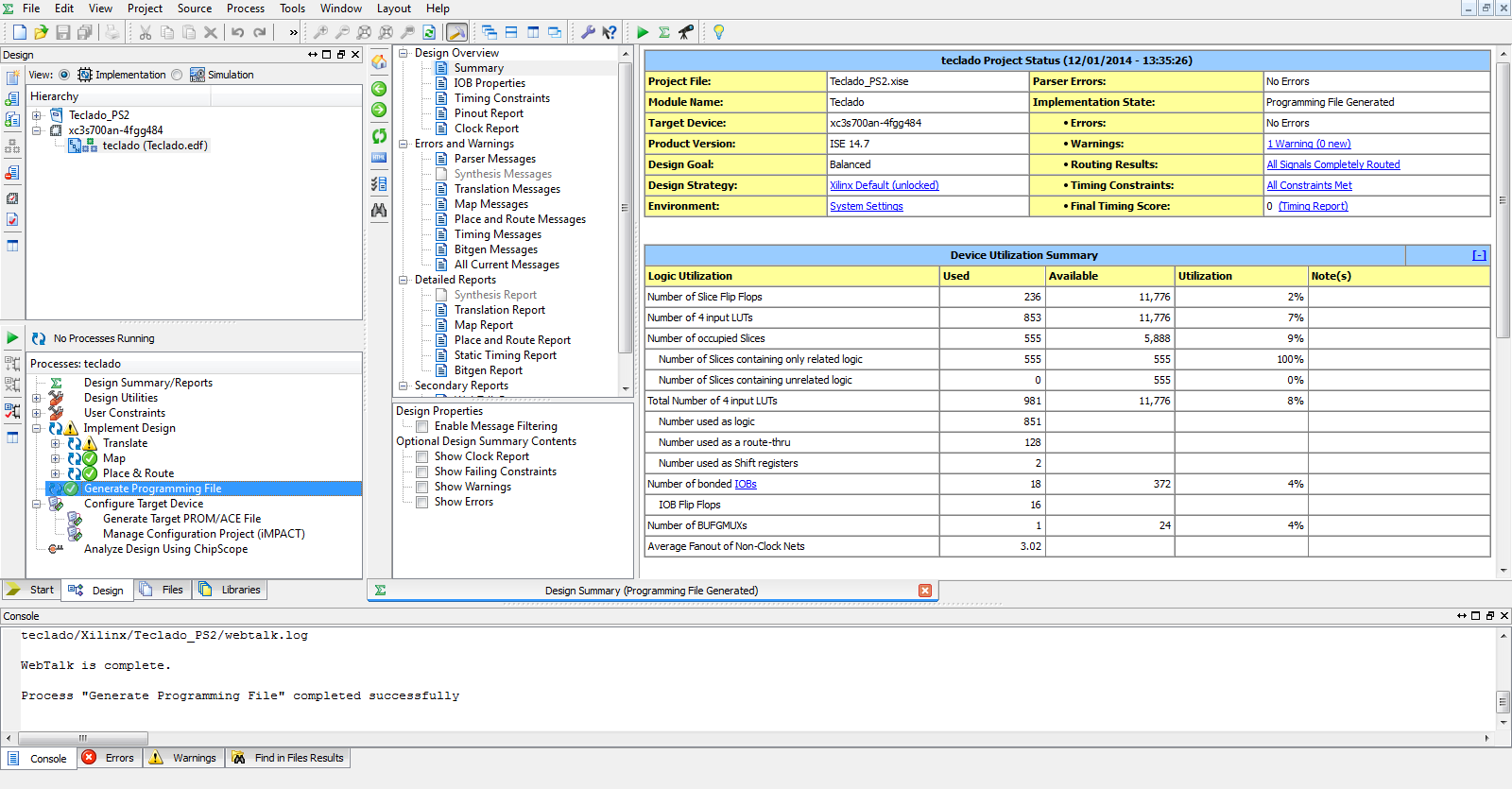

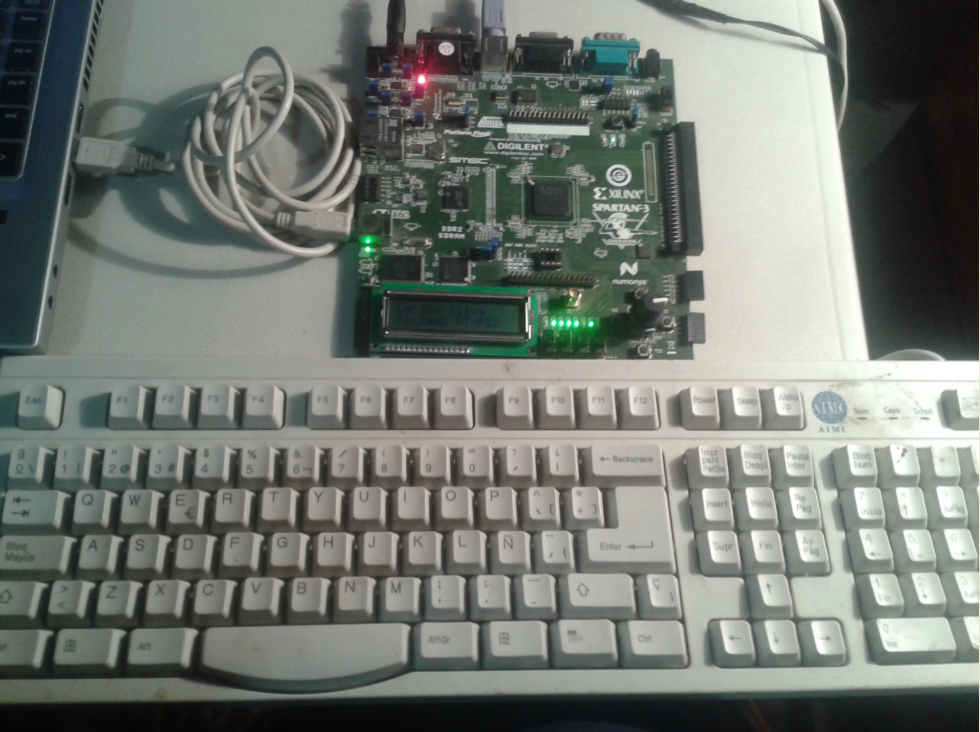

- Las herramientas necesarias para realizar estos ejemplos son:

Ø Xilinx Design Tools ISE Suite 14.7

Ø DK Desing suite 5.0 SP5

Ø Synplify Pro H-2013.03

Ø Tarjeta Spartan 3AN (XC3S700AN)

- El siguiente esquema muestra el

proceso de obtención del archivo final suma.bit para el FPGA

Pasos:

I.

Hacer

un nuevo proyecto en DK Handel-C llamado suma. El código de main.hcc es el

siguiente:

#include

"delay.hch"

set clock = external "E12";

unsigned 8 LEDS,n,m;

interface bus_out() salida(LEDS) with

{data =

{"W21","Y22","V20","V19","U19","U20","T19","R20"}};

interface AddVHDL(unsigned 8

z)

AddVHDL(unsigned 8 x = n, unsigned 8 y = m) with

{vhdl_type = "std_logic_vector",busformat="B(I)"};

void main(void)

{

par

{

while(1)

{

LEDS = AddVHDL.z;

}

while(1)

{

par

{

n++;

m++;

}

delay_ms(C_MHZ,1000);

//1000 ms

}

}

}

CONFIGURACIÓN DK

I. II. Hacer un proyecto en ISE de

Xilinx llamado suma y agregar los archivos AddVHDL.vhd, main_hcc.vhd,

agility.vhd, suma.vhd, suma.ufc.

I. III. Cambiar

en la línea 197 del archivo main_hcc.vhd I0_AddVHDL_main_32

: AddVHDL por I0_AddVHDL_main_32 :

entity work.AddVHDL. Después guardar e implementar todo el proceso.

- Implementación satisfactoria.