En este apartado pretendemos

explicar la manera de utilizar módulos diseñados en VHDL dentro de código

Handel-C que estará escrito y compilado con DK (y por tanto se ejecutará en la

FPGA al programarla con él “.bit” resultado de todo este proceso). De esta

manera podremos pasar como entrada de un módulo valores obtenidos en el código

Handel-C y utilizar los valores de salida de dicho modulo para realizar otros

cálculos en el código escrito en Handel-C.

Para comunicar el código Handel-C con VHDL ha sido necesario

utilizar una definición de interface que se ajustara a la entidad de VHDL, con

lo que conseguimos una instancia de esta interface así como definir los datos

que serán transmitidos, tanto hacia la entidad VHDL como desde ella. La

definición de un interface sigue el siguiente formato:

interface nombre_entidad_VHDL

(puerto_salida_entidad [with especificación_puerto]

{, puerto_salida_entidad [with especificación_puerto]})

nombre_instancia

(puerto_salida_entidad [with especificación_puerto]

{, puerto_salida_entidad [with especificación_puerto]})

with {busformat = “tipo_busformat”};

Donde tipo_busformat puede tomar los siguientes valores: “B”, “B[I]”,

“B(I)”, “B<I>”, “BI”, “B_I” , “B[N:M]” , “B(N:M)” , “B<N:M>” ,

“B[N]” , “B(N)” y “B<N>” Así, tendremos que hacer tantas definiciones de

interface de una entidad VHDL como instancias de dicha entidad queramos

utilizar en nuestro código Handel-C, es decir, si quisiéramos tener dos

instancias de un determinado tipo de entidades, tendríamos que hacer dos

definiciones de su interface.

Hay que tener muy en cuenta que el

nombre de la interface en el código Handel-C y de la entidad en el VHDL, los

nombres de los puertos en ambos sitos y el orden de los mismos debe ser

idéntico. Otra cosa en la que hay que fijarse mucho (si no, nos dará error al

generar el “.bit” en el Project Navigator) es en el valor que pongamos en el “busformat” al crear los archivos VHDL

finales o bien un EDIF con el DK.

El “busformat” sirve para indicar el nombre que se va a generar en el

EDIF para cada componente de un vector de la entidad VHDL definida en la

interface Handel-C. Por ejemplo, si uno de los puertos de nuestra entidad VHDL

es de la forma salida std_logic_vector (3 downto 0), para que los archivos de

salida sean generados con los nombres correctos (salida(0), salida(1), ...) es

necesario poner en la definición del interface with {bus_format = “B(I)”}.

Se tienen 2 maneras para obtener el

archivo final .bit del FPGA, las cuales se enuncia a continuación:

1) Todos los archivos fuentes del proyecto son

VHDL

2) Archivo EDIF por DK y archivo NGC del

módulo VHDL a integrar sintetizado por XILINX.

- Desarrollemos las 2 formas de realizar este proceso por medio de un ejemplo para dos plataformas, una para XILINX y otra para ALTERA.

El ejemplo consistirá en integrar un CORE VHDL de un sumador de 8

bits llamado AddVHDL.vhd cuyo código fuente es:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity AddVHDL is

Port ( x : in STD_LOGIC_VECTOR (7 downto 0);

y : in

STD_LOGIC_VECTOR (7 downto 0);

z : out STD_LOGIC_VECTOR (7 downto 0));

end AddVHDL;

architecture Behavioral of AddVHDL

is

begin

z

<= x + y;

end Behavioral;

- Las herramientas necesarias para realizar estos ejemplos son:

Ø Xilinx Design Tools ISE Suite 14.7

Ø DK Desing suite 5.0 SP5

Ø Synplify Pro H-2013.03

Ø Quartus II 13.1

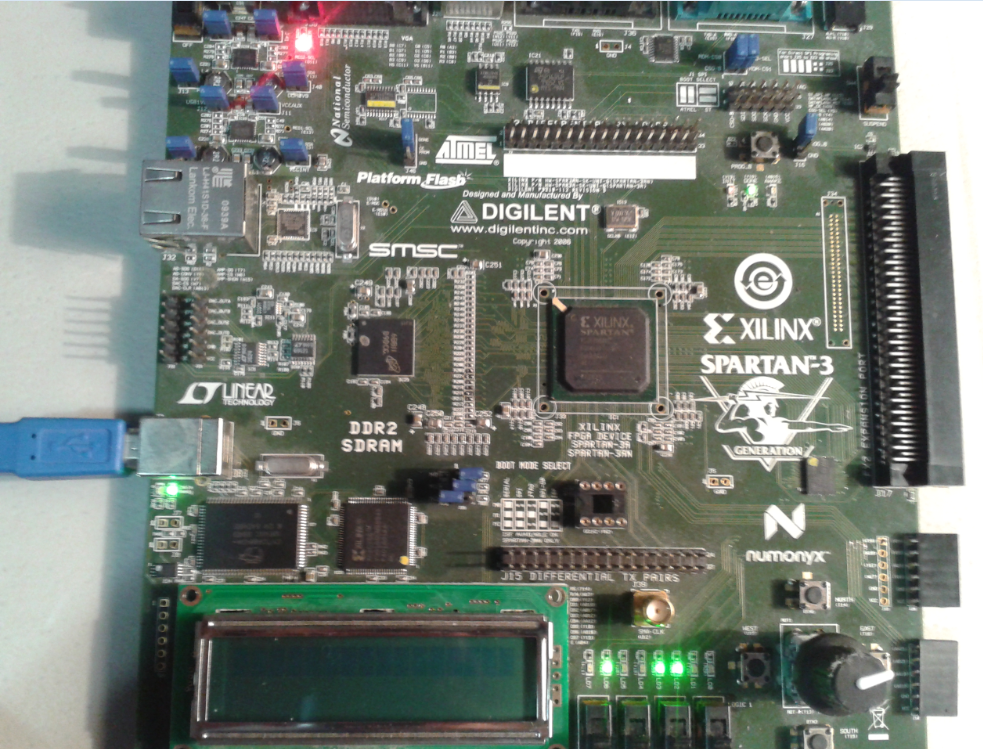

Ø Tarjeta Spartan 3AN (XC3S700AN)

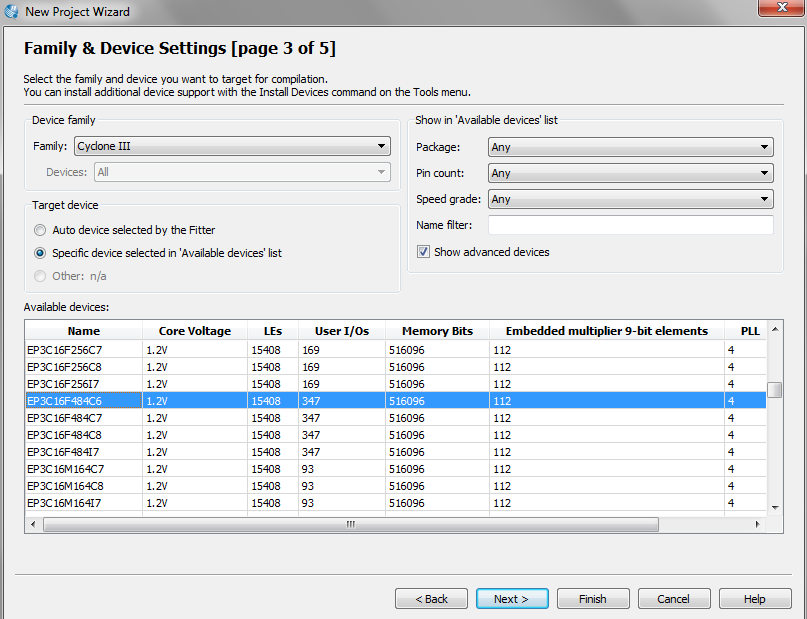

Ø Tarjeta DE0 ALTERA (EP3C16F484C6N)

- Ejemplo 1.- Plataforma XILINX todos los archivos son VHDL

- Pasos:

I.

Hacer

un nuevo proyecto en DK Handel-C llamado suma. El código de main.hcc es el

siguiente:

#include "delay.hch"

set clock = external "E12";

unsigned 8 LEDS,n,m;

interface bus_out() salida(LEDS) with

{data =

{"W21","Y22","V20","V19","U19","U20","T19","R20"}};

interface AddVHDL(unsigned 8

z)

AddVHDL(unsigned 8 x = n, unsigned 8 y = m) with

{vhdl_type = "std_logic_vector",busformat="B(I)"};

void main(void)

{

par

{

while(1)

{

LEDS = AddVHDL.z;

}

while(1)

{

par

{

n++;

m++;

}

delay_ms(C_MHZ,1000);

//1000 ms

}

}

}

Configuraciones de DK Handel-C

II. Hacer un proyecto en ISE de

Xilinx llamado suma y agregar los archivos AddVHDL.vhd, main_hcc.vhd,

agility.vhd, suma.vhd, suma.ufc.

III. Cambiar

en la línea 197 del archivo main_hcc.vhd I0_AddVHDL_main_32

: AddVHDL por I0_AddVHDL_main_32 :

entity work.AddVHDL. Después guardar e implementar todo el proceso.

- Ejemplo 2.- Plataforma XILINX archivo EDIF por DK y archivo NGC del módulo VHDL.

- Pasos:

I.

Utilizando

el mismo código del Ejemplo 1 anterior. La única variante es en las propiedades

de DK cambiar de VHDL a EDIF. En la pestaña superior cambiar a EDIF y por

ultimo construir el proyecto.

II. Crear un nuevo proyecto en ISE

de XILINX escogiendo XST como opción de síntesis y agregar el archivo

AddVHDL.vhd. En las propiedades de síntesis deshabilitar la opción “Add I/O buffers”

y por ultimo correr el proceso solo de síntesis.

III. Crear

otro proyecto con ISE de XILINX para conjuntar los archivos EDIF generado por

DK Handel-C y NGC generado a partir del módulo VHDL sintetizado en el paso 2.

·

Seleccionar

EDIF como fuente de archivo TOP.

·

Importar

el archivo EDIF ubicado en la carpeta de proyecto DK Handel-C

·

Copiar

el archivo AddVHDL.NGC que se genero en ISE de XILINX cuando se sisntetizo el

archivo VHDL a la nueva carpeta de proyecto.

·

Correr

todo el proceso de implementacion.

- Ejemplo 3.- Plataforma ALTERA todos los archivos son VHDL

- Pasos:

I.

Generar

los archivos VHDL en DK Handel-C con las opciones para la plataforma Altera.

Tarjet Family AletarCycloneIII y HDL

output Style SynplifyPro.

II. Hacer

un proyecto en QUARTUS II de Altera llamado suma y agregar los archivos AddVHDL.vhd, main_hcc.vhd, agility.vhd, suma.vhd, suma.tcl.

III. Correr

el script suma.tcl

IV.

Clic

derecho en el archivo agility.vhd y en propiedades escribir en Library:

agility.

V.

Cambiar

en la línea 195 del archivo main_hcc.vhd I0_AddVHDL_main_32

: AddVHDL por I0_AddVHDL_main_32 :

entity work.AddVHDL. Después guardar e implementar todo el proceso de compilación. Y por último programar el FPGA.

Handel-C language

reference.

No hay comentarios.:

Publicar un comentario